LibWiz

Library analysis and generation

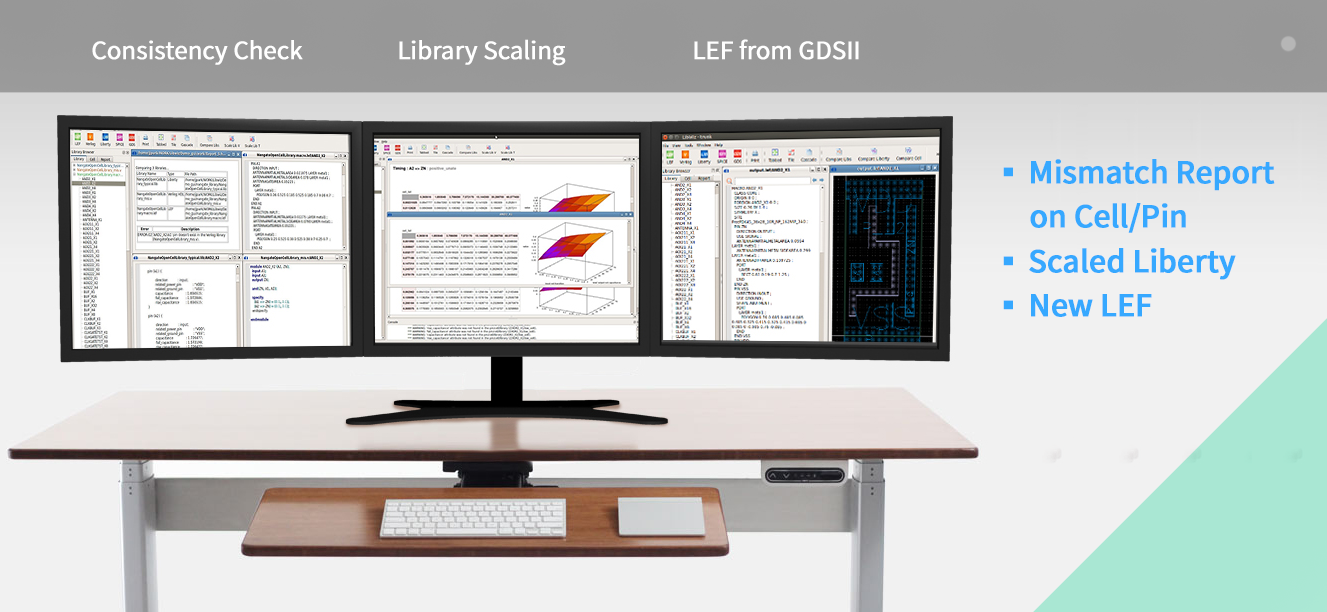

LibWiz provides consistency check between different library format for standard cell, I/O cell, and IP cell which is very challenging in SoC design flow. This feature helps designers to keep the consistency of different format along the library in terms of pin name/direction bus width, and cell presence, etc., and finally reduces their workloads significantly. LibWiz also facilitates liberty library scaling which enables designers to characterize new one for various conditions. Generation of LEF abstract template from the GDSII library of standard/Pad/IP cell is another indispensables which helps work during the flow without LEF.

Features

- Consistency check of the libraries( Liberty, Verilog HDL, LEF, GDSII, and Spice ) and report on the mismatch for cell name and pin direction/name

- Library generation by scaling for voltage and temperature conditions

- LEF template generation from GDSII library under graphic visualization

- Automatic validation check of lookup table ranges and indices of the Liberty library

- Liberty timing arc validation against functional Verilog HDL

Benefits

- Comprehensive and easy to identify inconsistency problems

- High quality scaled library for various conditions

- Both GDSII/LEF viewer for easy cross-check

- Fast and easy LEF template generation from GDSII library

- Powerful graphic and TCL-based user interface